1. 순서논리회로의 개요

조합논리회로: 현재 시간의 입력에 의해 출력이 결정

순서논리회로: 조합논리회로에 저장요소를 추가한 회로

순서논리회로는 외부로부터 2진 정보를 전달받게 되고, 이 외부로부터의 입력은 저장요소에 저장된 현재 상태와 함께 출력의 2진 값을 결정한다.

비동기 순서논리회로

- 시간지연소자를 사용

- 시간지연소자는 신호가 전달되려면 일정한 시간이 걸리므로 기억능력을 갖게 됨

- 논리게이트로 구성되는 시간지연소자는 게이트간의 피드백 때문에 예측 못한 상태로 동작하거나, 불안정한 상태가 발생되기도 함

- 이러한 이유로 자주 사용되지 않음

동기 순서논리회로

- 특정 순간에서만 저장요소를 내용을 변화시킬 수 있는 신호를 사용 -> 클럭 펄스 (1과 0으로 이루어져 있음)

- 이러한 클럭 펄스는 시스템 전체에 제공

- 이처럼 저장요소 입력에 클럭 펄스를 제공하는 동기 순서논리회로를 클럭을 가진 순서논리회로라고 한다.

- 플립플롭이라는 저장요소를 사용하며, 가장 많이 사용되는 순서논리회로

플립플롭(F/F: Flip Flop)

- 입력신호에 의해 상태를 바꾸도록 지시가 있을 때까지 현재의 2진 상태를 유지하는 논리소자

- 한 비트의 2진 정보를 저장할 수 있는 장치

- 클럭 신호에 의해 출력상태를 바꾼다.

종류

- SR 래치

- 넓은 의미의 플립플롭

- 구동방법이 다름(구동입력이 1일 때 출력이 바뀜)

- 비동기 순서논리소자

- RS 플립플롭, D 플립플롭, JK F/F, T F/F, 마스터-슬레이브 F/F

- 클럭신호에 의해 출력이 바뀜

- 동기 순서논리소자

2. 플립플롭

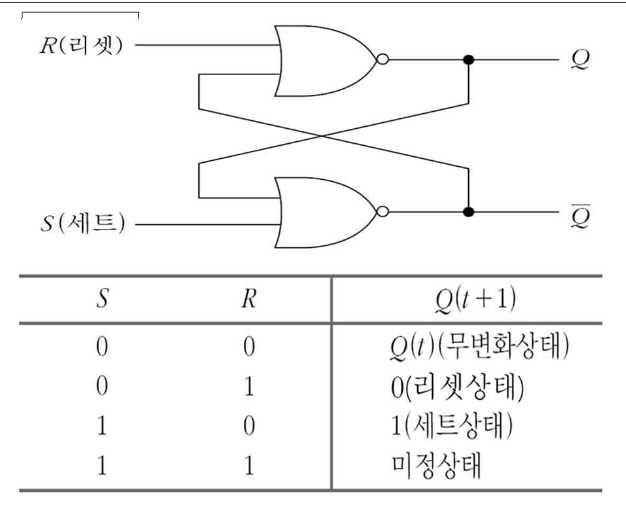

1) SR 래치(RS 플립플롭)

- 두 개의 NOR 게이트나 두 개의 NAND 게이트로 구성

- 각각 세트(set)와 리셋(reset)의 두 입력을 갖는다.

NOR 게이트로된 SR 래치

세트라고 하는 입력과 R이라고 하는 입력이 되어 있고 Q와 보수값 Q를 출력을 갖는다.

Set 쪽에 0 Reset 쪽에 0 => 앞선 출력을 그대로 유지한다. 무변화 상태

0 1 => 리셋 상태

1 0 => 세트 상태

1 1 => 미정상태

1과 1이 들어왔을 때 미정상태가 발생하는 것이 문제가 된다.

4가지 상태

무변화상태라는 것은 들어간 것이 그대로 나온 것

NAND 게이트로 된 SR 래치

0 0 => 미정 상태

0 1

1 0

1 1 => 무변화 상태

수행 기능은 동일

그러나 입력과 출력에 따른 동작은 반대

어쨌든 미정상태가 발생한다는 것이 가장 큰 문제이다.

또한 비동기 순서논리회로

=>

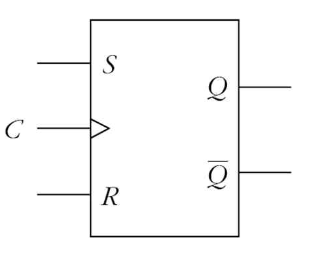

제어 입력을 가진 SR 래치(RS 플립플롭)

- SR 래치에 게이트를 추가하여 동작을 개선

- SR 래치가 한 클럭펄스 발생기간 동안 입력에 응답하도록 만들 수 있다.

- 즉, 클럭을 가진 래치 또는 RS 플립플롭이라고 함

NAND 게이트 혹은 NOR 게이트로 된 SR 래치 앞단에다가 클럭을 추가함

동기를 맞춰주기 위해서 클럭을 부과했다.

그런데 여전히 1 1 일때 미정 상태

그래픽 기호로는 다음과 같이 표현할 수 있다.

여전히 미정상태일 때 문제점

- 세 입력이 모두 1 일 때 어떤 값으로도 결정할 수 없는 상태 발생

- 이것은 내부 SR 래치의 양쪽 입력값을 모두 0 으로 만들어 내부 NAND 게이트를 미정상태로 만들기 때문

- 제어입력이 다시 0 으로 될 때는, 다음 상태는 두 입력 S, R 중 어느 것이 먼저 1로 되는가에 따라 결정되기 때문에 다음 상태를 정확히 예측할 수 없는 문제점 발생

-> D 플립플롭, JK 플립플롭 등이 제안됨

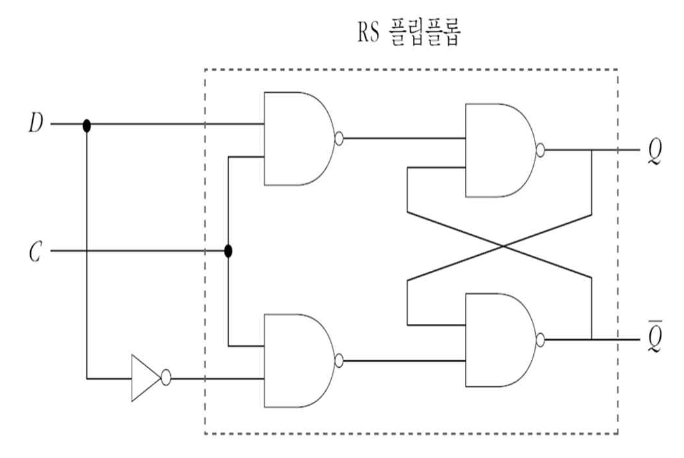

2) D 플립플롭

- RS 플립플롭의 문제점 해결을 위한 방법 (동시 1이 들어갈 때 미정상태가 되는)

-> S, R이 동시에 1을 갖지 않도록 한다.

입력을 하나만 쓰고 한쪽은 NOT 게이트를 이용해서 0 1 이 들어가도록 만들어줌

- D 플립플롭 : RS플립플롭의 한 변형

- D 입력은 RS 플립플롭의 S 입력으로 들어가고,

- R 입력으로는 NOT을 통한 D 입력의 보수값이 들어간다.

- NOT 게이트를 추가함으로써 입력이 2개에서 1 개로 줄어든다.

클럭이 0일 때 = > 무변화 상태

클럭이 1일 때 D 값의 변화에 따라 동작

- 제어입력 C 가 0인 경우 D 의 입력값에 관계 없이 D 플립플롭의 출력상태는 변하지 않고,

- 제어입력 C 가 1 일 때만 D 입력이 출력에 나타나게 된다.

- 즉, D 가 1 이면 세트상태, D 가 0 이면 리셋상태가 된다.

구체적인 의미는, 결국 입력으로 들어가는 값이 출력으로 그대로 나온다는 것이다.

입력 => 출력 그대로 전달

즉, 특성은 내부에 데이터를 저장하는 것과 같다.

3) JK 플립플롭

- RS 플립플롭의 미정상태 문제점을 개량한 형태

- 가장 많이 사용되는 플립플롭

S => J

R => K

각각 대응된다.

1 1이 들어왔을 때 미정상태가 아닌 보수 상태를 나타내준다.

=> RS 플립플롭의 개선

- JK 플립플롭의 J 와 K 가 모두 1인 때를 제외하고는 RS 플립플롭의 동작과 같다.

- J 와 K 가 모두 1인 경우의 다음 상태는 한 클럭 펄스 뒤에 현재 상태의 보수가 된다.

- 즉 Q(t) =1 이면 Q(t+1) = 0,

Q(t) = 0 이면 Q(t+1) = 1 이 된다.

- 그러나 J, K 가 모두 1 일 때 출력이 보수가 취해진 다음에도 클럭펄스가 남아있으면 반복적으로 보수를 취하는 문제점 발생

-> 레이스 현상

4) T 플립플롭

- JK 플립플롭의 변화된 형태

- 두 입력을 하나로 묶어서 만듬

- 명칭 T는 상태를 반전한다는 Toggle에서 유래

두 입력을 하나로 묶어준 형태

1이 들어오면 반전을 나타낸다.

3. 플립플롭의 트리거링

트리거

- 클럭이 남아 있는 상태에서 계속해서 반전 반전 반전 시키는 문제 : 레이스 현상

(입력 J, K가 모두 1일 때 클럭펄스가 남아 있게 되면 또 다시 보수를 취하는 반복적인 현상)

- 플립플롭의 상태는 제어신호(클럭신호)의 순간적인 변화에 따라 바뀐다.

- 이 순간적인 변화를 트리거라고 한다.

- 예를 들어, D 플립플롭은 제어 입력으로 클럭펄스가 사용되는데(0상태와 1상태 반복), 이 클럭펄스가 논리 1 레벨로 변활 때마다 트리거 된다. => 1인 상황에서 동작을 하는 것

=> 이러한 논리 1 레벨 트리거가 가진 문제점이 있음

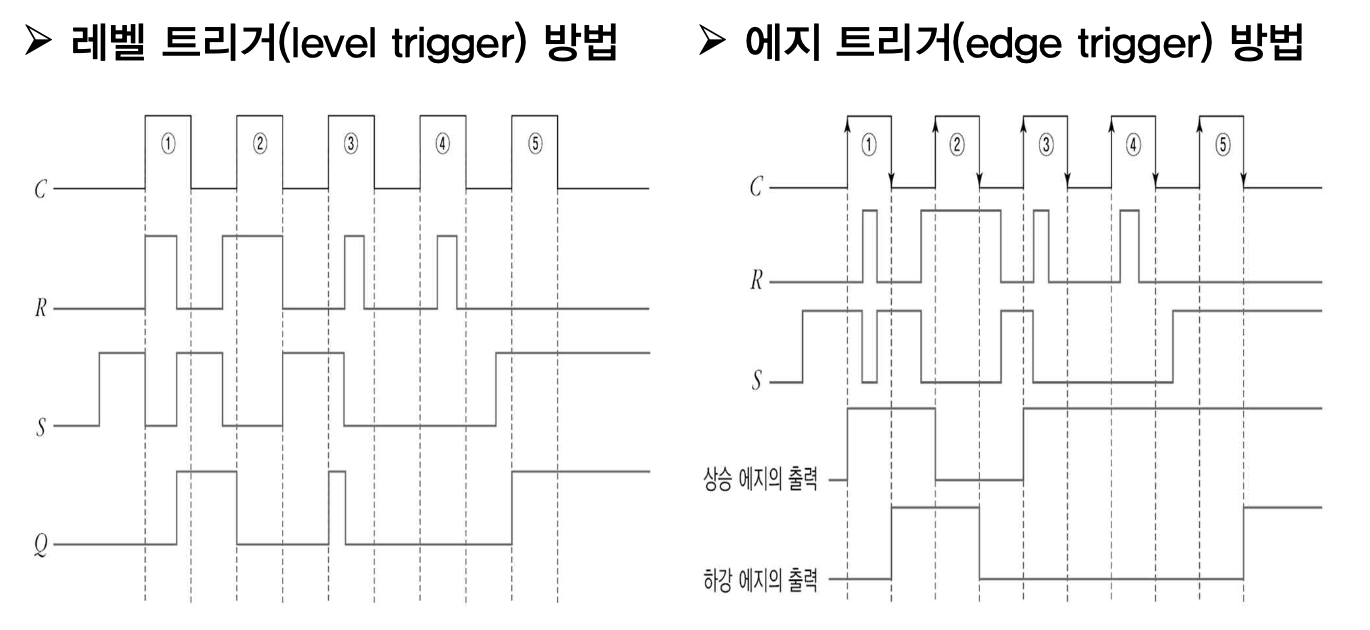

이러한 방법을 레벨 트리거 방법이라고 함

- 클럭펄스가 논리 -1 인 동안 내내 입력이 출력에 영향을 받음

에지 트리거 방법

- 클럭펄스의 에지, 즉 상승 에지나 하강 에지 동안에 입력이 출력에 영향을 미치게 된다.

- 상승 에지: 클럭펄스에 있어서 논리 상태가 논리 0 에서 논리 1로 천이하는 것

- 하강 에지: 반대로 논리상태가 논리 1 -> 논리 0

레벨 트리거 방법은 논리 상태 1일 때만 동작

에지 트리거 방법은 클럭 펄스마다 상승 에지와 하강 에지가 존재하는데 해당 에지마다 동작

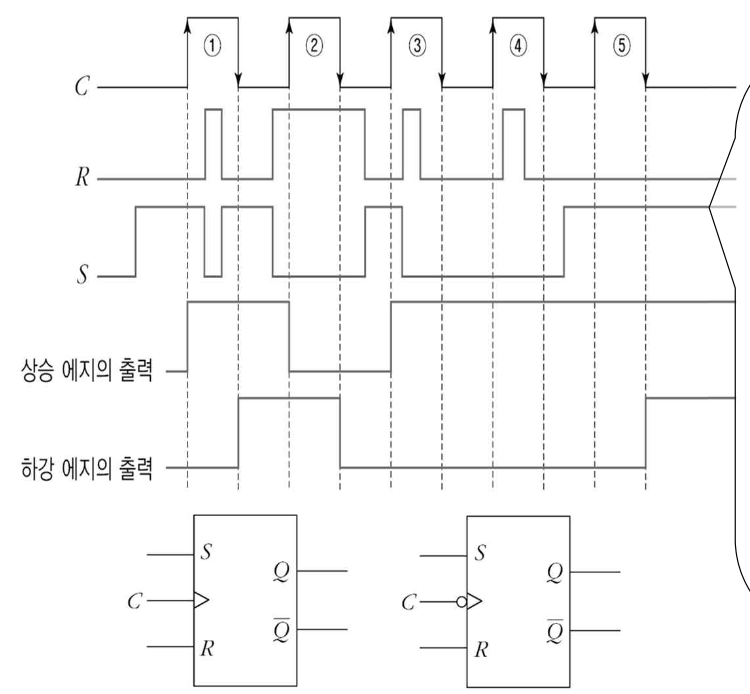

레벨 트리거 방식 RS 플립플롭 동작 특성

- 레벨 트리거 방법은 클럭펄스의 활동레벨, 즉 논리-1 상태 동안에서만 입력 변화에 따라 출력이 변화한다.

- 따라서 클럭펄스 1의 활동레벨 시작에서 보면 입력이 R=1, S=0이므로 출력은 Q=0 이 된다.

- 이때 클럭펄스 1의 논리-1 상태를 유지하는 중간부분에서 입력이 R=0, S=1 로 바뀌게 되므로 입력이 바뀌는 그 시점에서 출력 Q=1 상태로 파형이 바뀌게 된다.

- 다음으로 클럭펄스가 비 활동레벨, 즉 논리-0 상태 동안에는 전 상태가 유지

에지 트리거 방식

- 에지 트리거 방법은 클럭펄스의 에지,

즉 상승 에지나 하강 에지 동안에만 입력이 출력에 영향을 미친다.(클럭펄스가 1 또는 0 상태를 유지하는 동안은 무 동작)

- 우선 상승 에지 트리거 시 출력상태 변화를 보면, 클럭펄스 1의 상승 에지에서 R=0, S=1 이므로 출력은 세트상태를 나타낸다.

- 다음 클럭펄스 2의 상승 에지 시까지는 플립플롭이 입력의 변화에 따라 동작하지 않으므로 전 상태를 유지한다.

- 다음 클럭펄스 2의 상승 에지 시점에서 보면 R=1, S=0 이므로 출력은 리셋상태를 나타낸다.

레벨 트리거 방식

에지 트리거 방식

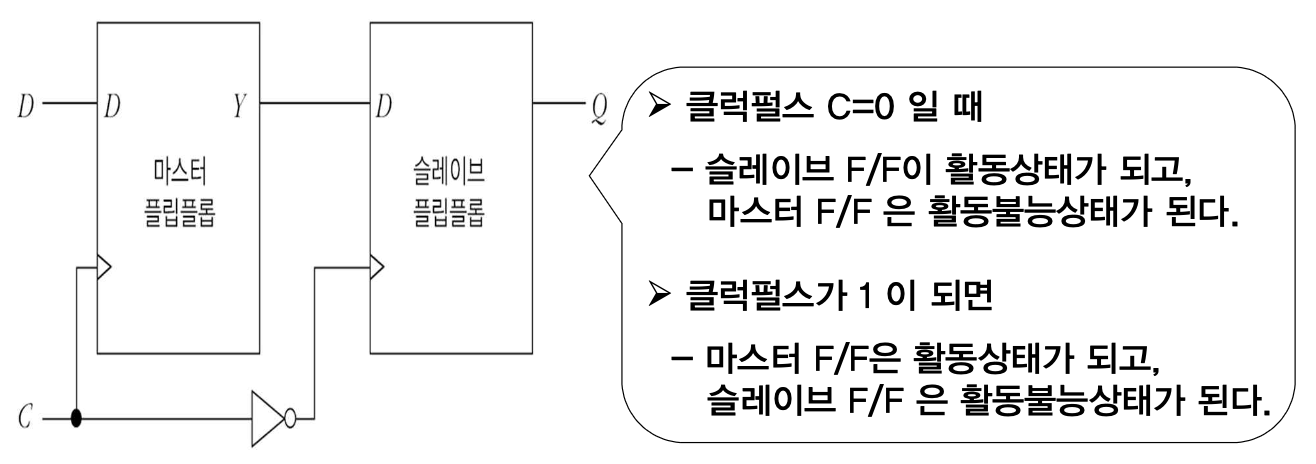

마스터 슬레이브 플립플롭

JK 플립플롭의 레이스 현상을 개선하는 방법으로 마스터 슬레이브 플립플롭이 제안됨

- 주(mater)와 종(slave)의 역할을 하는 두 개의 별도 플립플롭으로 구성

- 기존 플립플롭에 인버터를 추가하여 구성

마스터-슬레이브 플립플롭의 동작원리

- 클럭펄스의 상승 에지에서 첫 번째 플립플롭(마스터)를 세트하고,

- 클럭펄스의 하강 에지에서 두 번째 플립플롭(슬레이브)에 신호를 전달하도록 구성

두 개의 플립플롭을 장착하여 주, 종으로 사용함

RS 플립플롭을 이용한 마스터-슬레이브 플립플롭

- 클럭펄스 C=0 일 때

-> 슬레이브 F/F의 클럭입력이 1 이 되기 때문에 활동상태가 되어,출력 Q는 Y와같고, ~Q는 ~Y와 같아진다.

-> 이 때 클럭펄스 C=0 이기 때문에 마스터 F/F 은 활동불능상태(disable)가 된다.

- 클럭펄스가 1 이 되면

-> 외부 R 과 S 에 있던 정보가 마스터 F/F 에 전달되고,

-> 이 때 NOT 게이트의 출력은 0 이기 때문에 슬레이브 F/F 은 활동불능상태이다.

-> 결국 마스터 F/F과 분리된다.

=> 즉 교대로 동작하게 된다.

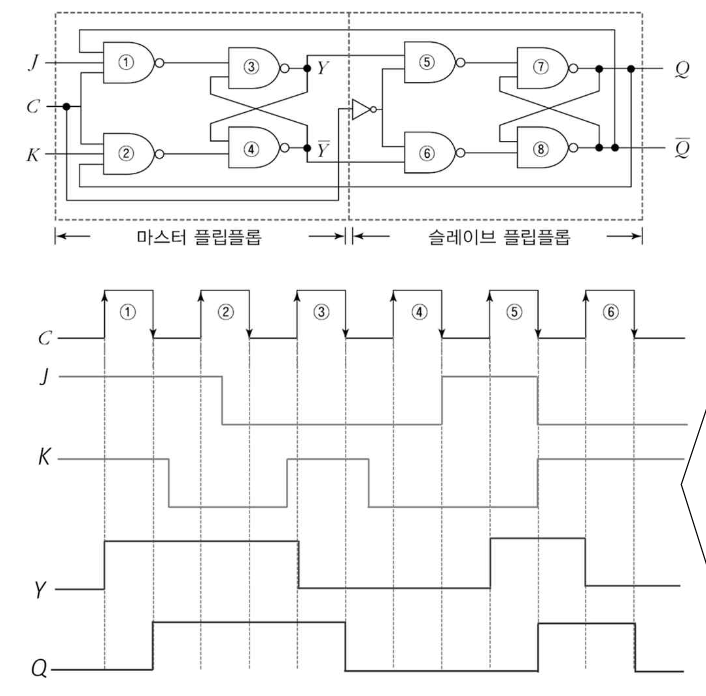

D플립플롭을 이용한 마스터-슬레이브 플립플롭

클럭펄스 1의 상승 에지 시점에서 보면

- 마스터 F/F은 세트상태이고,

- 외부입력 D=1 이므로 마스터 F/F의 출력 Y =1

- 이때 슬레이브 F/F은 활동불능 상태이므로 마스터 F/F의 출력이 슬레이브 F/F에 전달되지 못한다.

- 따라서 전체 출력 Q 는 아직 0 의 값이다.

다음으로 클럭펄스 1의 하강 에지 시점에서는

- 슬레이브 F/F이 활동상태가 되어,

- 마스터 F/F의 출력 Y 값이 슬레이브 F/F에 전달되어 전체 F/F의 출력 Q 는 1 상태가 된다.

- 물론 이때 외부입력 D 의 값이 0으로 변하지만, 이 순간 마스터 F/F은 활동불능 상태이므로 이 입력값은 다음의 클럭펄스의 상승 에지 시까지 영향을 미치지 못한다.

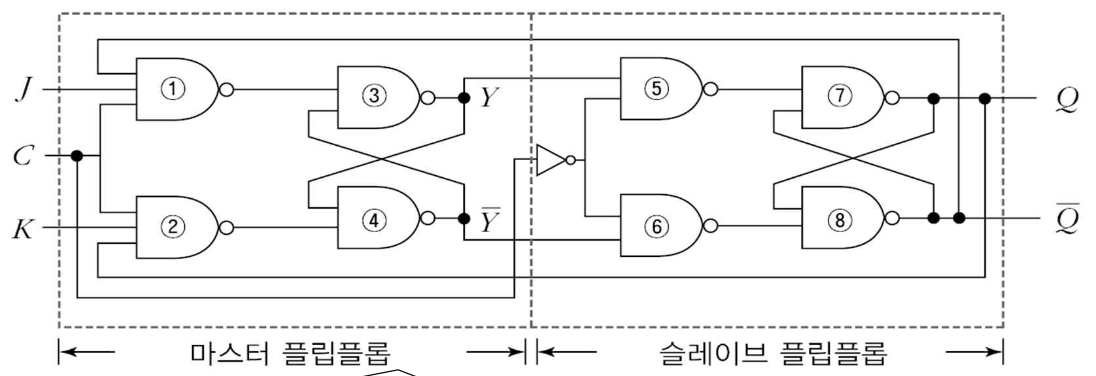

JK 플립플롭을 이용한 마스터-슬레이브 플립플롭

J 와 K 의 입력은

- 클럭펄스의 상승 에지에서 마스터 F/F에 전달되고, 클럭펄스의

하강 에지에서 슬레이브 F/F에 전달된다.

- 즉 J 와 K 의 입력은 클럭펄스의 상승에지 시에 들어오지만, 클럭펄스의 하강 에지 시까지는 전체 출력에는 나타나지 않는다.

-> 따라서 전체 F/F의 출력은 클럭펄스의 하강 에지에서 나타난다.

동작 원리

클럭펄스 1의 상승 에지에서

- 마스터 F/F 동작(J =1, K =1 이므로 반전) - 출력 Y 는 1 값을 갖는다.

- 이때 Q는 슬레이브가 비활성이므로 전달 받지 못함

클럭펄스 1의 하강 에지에서

- 슬레이브 F/F 동작(Y =1,~Y=0 이므로)

- 출력 Q 는 1 값을 갖는다.

클럭펄스 2의 상승과 하강 에지에서

- 마스터 F/F Y=1, 슬레이브 F/F Q=1

클럭펄스 3의 상승과 하강 에지에서

- 마스터 F/F Y=0, 슬레이브 F/F Q=0

계속해서 클럭의 상승과 하강 에지에서

- 마스터 F/F과 슬레이브 F/F이 활동과 비활동의 상태로 동작

참고자료: 디지털논리회로(김형근, 손진곤 공저, KNOU press 출판)

'CS > 디지털논리회로' 카테고리의 다른 글

| 순서논리회로의 설계 과정 및 예시, D 플립플롭, JK 플립플롭 입출력 방정식 및 상태표 작성 (0) | 2023.06.15 |

|---|---|

| 순서논리회로의 분석, 상태표, 상태도 (0) | 2023.06.15 |

| 코드 변환기, 패리티 발생기/검사기, BCD-세븐 세그먼트 표시기, 인코더 (0) | 2023.06.14 |

| MSI를 이용한 조합논리회로, 디코더, 멀티플렉서, 디멀티플렉서 (1) | 2023.06.14 |

| 4변수 카르노 도표, 무관 조건, 기타 카르노 도표, NADN 게이트와 NOR 게이트를 이용한 논리회로 구현 (0) | 2023.06.14 |