1. 동기식 카운터

비동기식 카운터

- 구조가 간단하고 동작이 단순

- 동시에 트리거되지 않으므로 속도에 제약

동기식 카운터

- 모든 F/F에 동시에 클럭이 가해짐

- 한번에 동작되므로 동작 속도의 향상

-> 2진 카운터, 모듈로-N 카운터

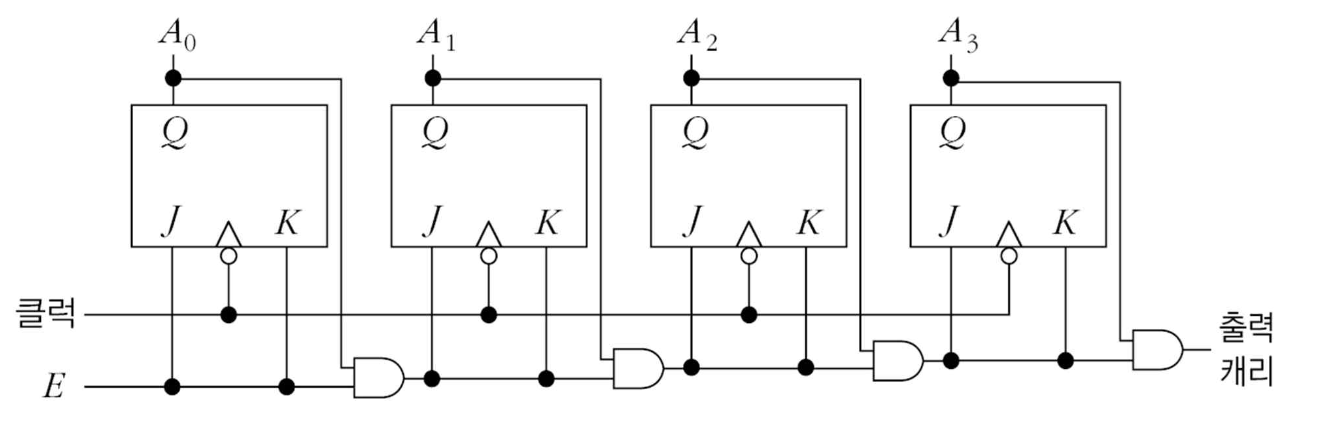

(1) 2진 카운터: 2진 순서를 따르는 카운터

4비트 동기식 2진 카운터 (상향계수 : 0 ~ 15 순서대로 계수)

4개의 JK 플립플롭 이용

일반적으로 4비트를 표현할 때 A3부터 표현

아래 그림은 방향을 바꿔놓은 그림

4비트 2진 카운터의 현재상태가 A3 A2 A1 A0 = 0011 라면 다음상태는 0100으로 바뀌어야 함 (10진수로 3 -> 4)

E=1이면, A0 는 클럭펄스가 입력될때 마다 보수를 취하므로 0이 되고,

A1 은 A0의 현재 상태가 1이기 때문에 보수를 취하므로 0이 된다.

A2 는 A1 A0의 현재상태가 11이므로 보수를 취해 1이 된다

A3 는 A2 A1A0의 현재 상태가 011로 모두 1이 아니므로 0이 된다.

0011 -> 0100 으로 변화

(2) 모듈러-N 카운터

- N개의 계수 순서(0, 1, 2 ... , N-1)를 반복하여 계수하는 카운터

- 모드-N 카운터 라고도 함

예) 모듈로-16 카운터 : 0부터 15까지 계수하는 카운터

☞ BCD카운터 = 모듈로 10 카운터

모듈러-8 카운터: 0부터 7까지

3개의 출력 단자

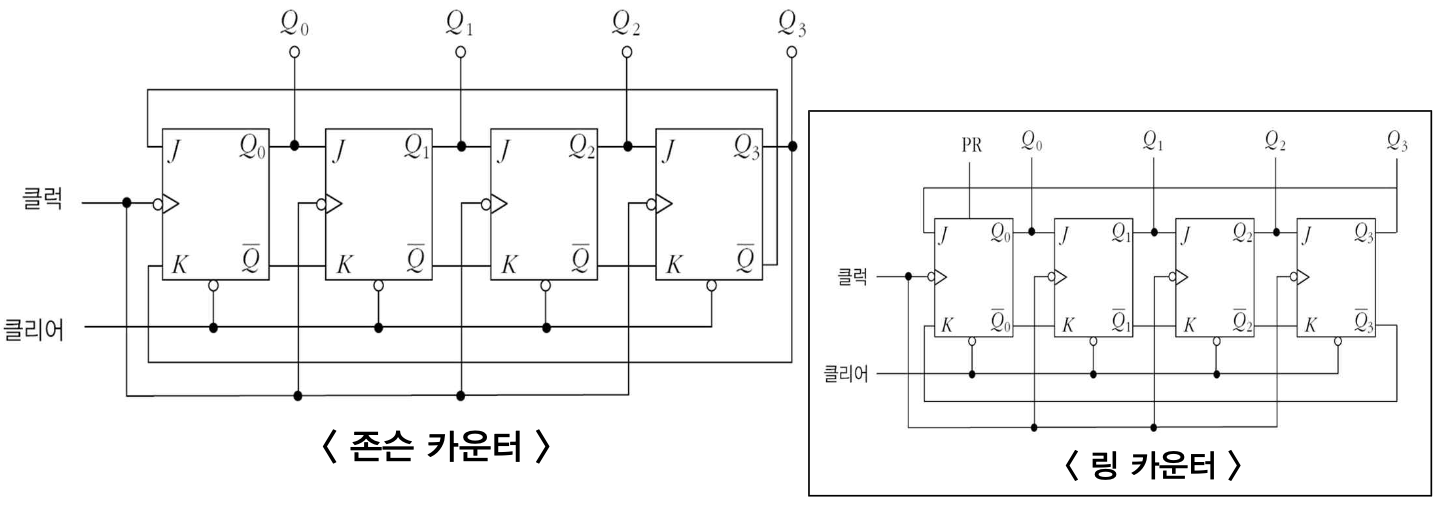

2. 시프트 카운터

시프트 카운터

- 시프트 레지스터의 동작을 응용한 카운터

시프트 카운터의 예

- 링 카운터

- 존슨 카운터

링 카운터의 문제점을 해결한 것이 존슨 카운터임

(1) 링 카운터

- 출력 비트 중 한 비트만 1 이 되고 입력펄스에 의해 한쪽 방향으로 1 의 위치가 순환

- 디코더의 출력을 보면 2x4라고 하면 입력이 2개, 출력이 4개 -> 어느 하나만 1을 갖고 나머지는 0을 가졌었다. 카운터도 마찬가지로 출력 비트 중 1개만 1이 된다.

1의 위치가 바뀜

어떻게 보면 다른 카운터에 비해서 의미가 없어보일 수 있지만, 특정 동작을 수행하는 경우에 많이 사용될 수 있다.

JK 플립플롭으로 구성

PR(preset)과 클리어 신호를 이용해서 첫번째 F/F Q0를 항상 1로 하고 나머지 F/F은 0으로 한 상황에서 동작을 한다.

그러면 처음의 1000 의 신호가 시프트 동작에 의해 하강클럭 때 마다 0100, 0010, 0001, 1000, ... 으로 자리이동을 한다.

하강 클럭시마다 1의 위치가 바뀜.

일반적으로 N개의 F/F으로 구성된 링 카운터는 N가지의 출력상태를 나타낸다.

(2) 존슨 카운터

- 링 카운터와 유사

- 2배 -> 상태수를 늘려주었다는 장점

- 디코더가 부수적으로 필요해지는 단점

- 다른 점은 첫 번째 F/F 의 J, K 입력에 피드백되는 네번째 F/F의 Q와 ~Q가 반대로 연결

링카운터는 맨 마지막 단에 Q 값이 첫 번째 의 J로 피드백이 되었는데 존슨 카운터는 ~Q가 연결되어 있다.

클리어 신호에 의해

Q0Q1 Q2 Q3 =0000이라면

-> 첫클럭에서 Q0Q1Q2Q3=1000이된다.

-> 두 번째, 세 번째, 네 번째 클럭에서 Q0 Q1 Q2 Q3 은 1100, 1110, 1111 이 된다.

-> J = 0 이므로 출력은 0111 이 된다.

-> 이 후 앞의 과정 반복

앞의 링카운터보다 2배의 상태 변화를 나타낸다.

즉, N개 F/F -> 2N 개의 출력 상태

3. 카운터의 설계

동기식 카운터 설계는 순서논리회로 설계와 동일

동기식 카운터 설계 예

- 2진 카운터

- BCD 카운터

- 임의의 순서를 가진 카운터

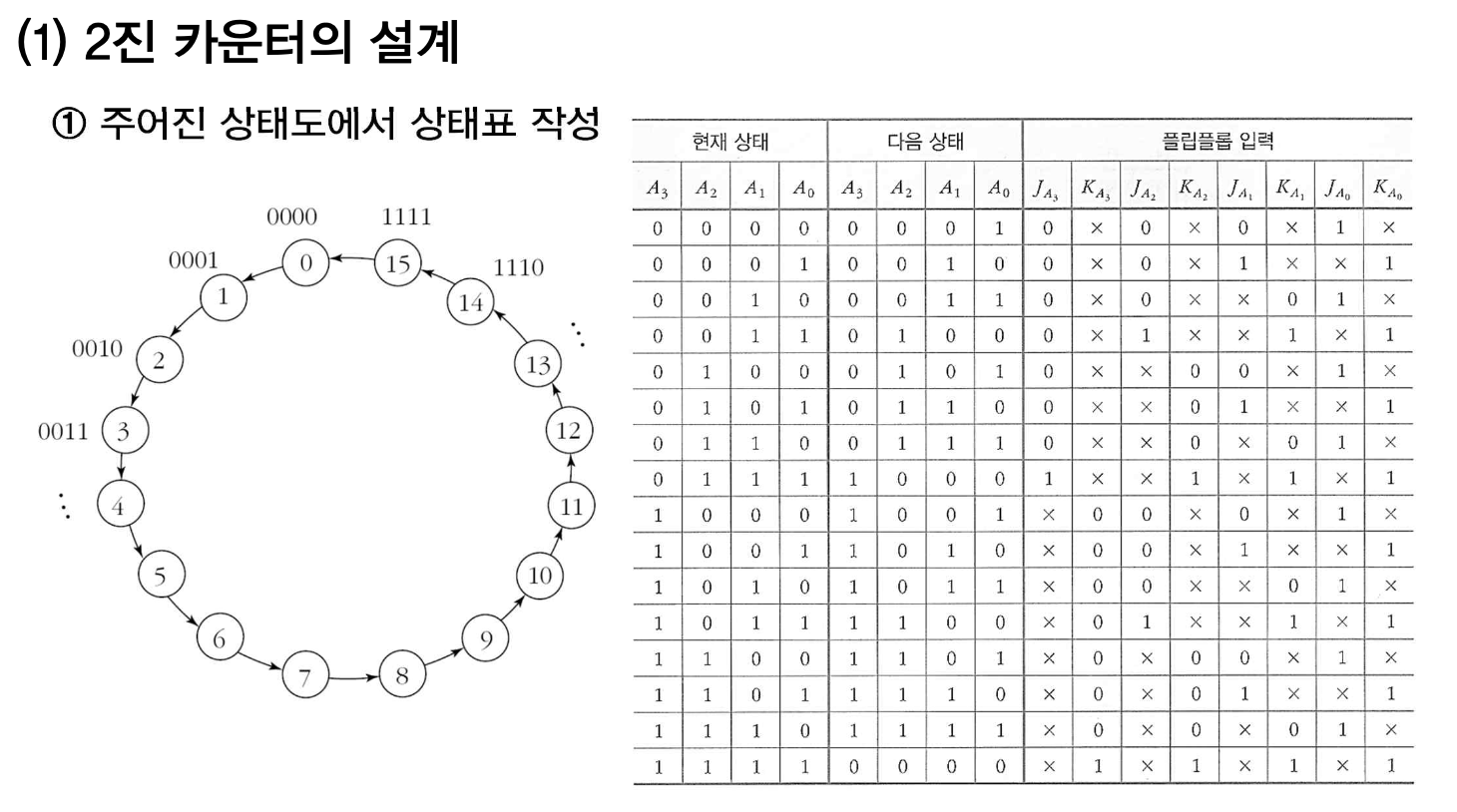

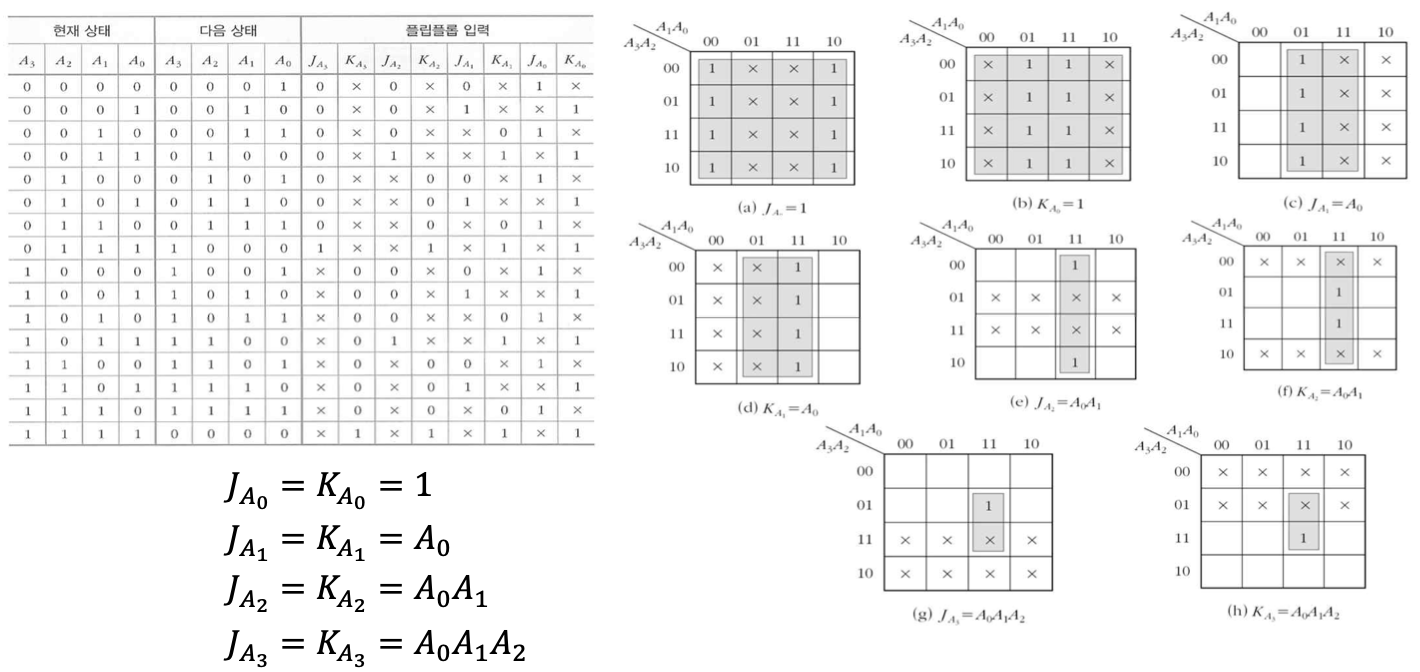

(1) 2진 카운터

상태표에서 카르노 도표를 이용하여 입력방정식 유도

입력 방정식을 이용해 논리도 작성

(2) BCD 카운터

주어진 상태도에서 상태표 작성

상태표에서 카르노 도표를 이용해 입력방정식 유도

입력 방정식을 이용해 논리도 작성

출력 Y는 BCD 카운터를 직렬 연결할 때 한자리 높은 카운터의 계수입력을 위해 사용

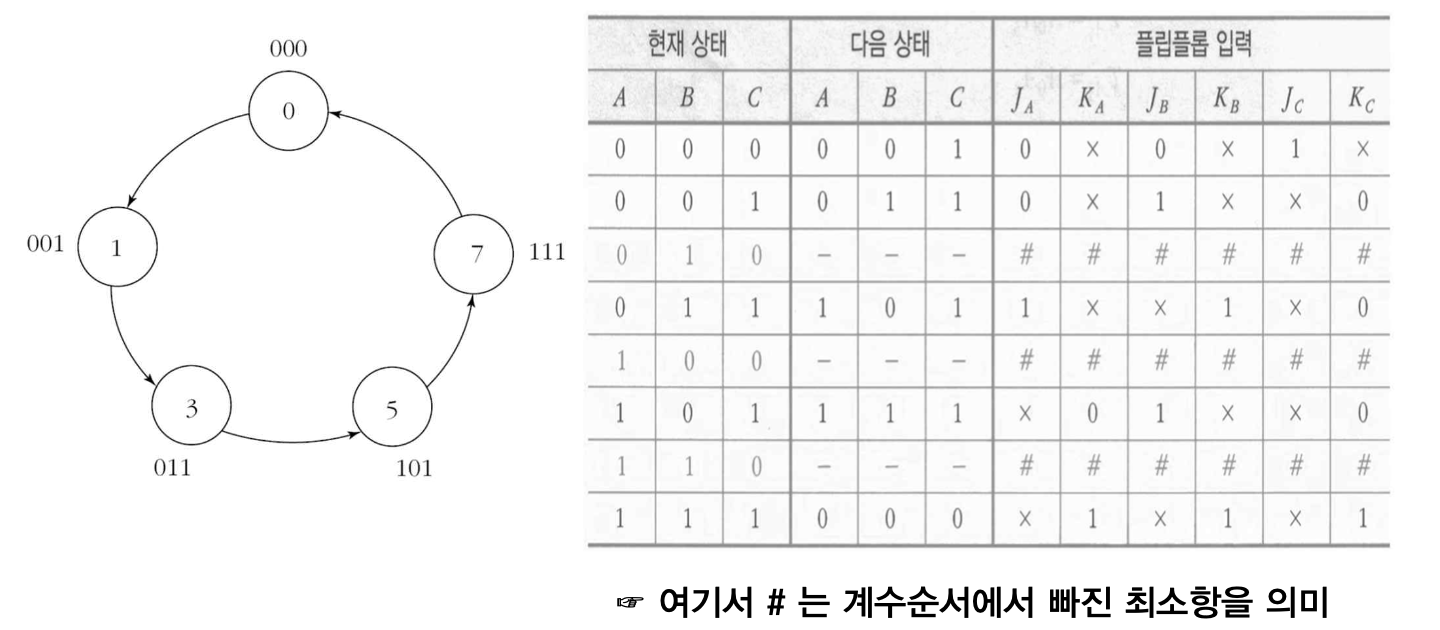

(3) 임의의 순서를 가진 카운터의 설계

주어진 상태도에서 상태표 작성

상태표에서 카르노 도표를 이용하여 입력방정식 유도

입력방정식을 이용하여 논리도 작성

참고자료: 디지털논리회로(김형근, 손진곤 공저, KNOU press 출판)

'CS > 디지털논리회로' 카테고리의 다른 글

| PLD의 구조와 종류, PLA의 내부구조, PLA를 이용한 부울함수, PAL의 내부구조, PAL을 이용한 부울함수 구현 (0) | 2023.06.15 |

|---|---|

| 기억장치와 PLD, RAM의 구성, RAM의 확장 방법, ROM의 구성, ROM을 이용한 조합논리회로 구현 (0) | 2023.06.15 |

| 레지스터, 데이터 적재 레지스터, 시프트 레지스터, 카운터, 비동기식 카운터 (0) | 2023.06.15 |

| 순서논리회로의 설계 과정 및 예시, D 플립플롭, JK 플립플롭 입출력 방정식 및 상태표 작성 (0) | 2023.06.15 |

| 순서논리회로의 분석, 상태표, 상태도 (0) | 2023.06.15 |